(URIOUS

CL12451IP135

## LVDS Transmitter 18bit FPD-link 135MHz (max: 170MHz) Single

## **Introduction**

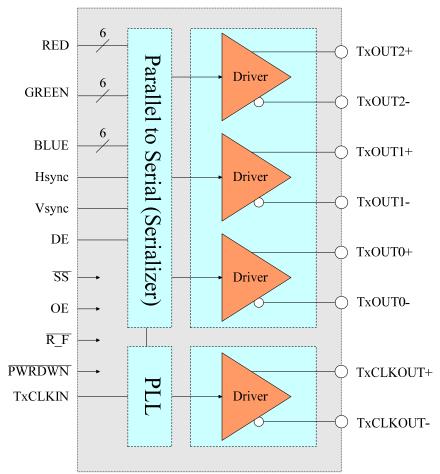

The CL12451IP135 transmitter converts parallel 21bits (18bits of RGB data and 3bits of HSYNC, VSYNC, DE) of LVCMOS parallel data into serial three LVDS data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. The CL12451IP135 transmitter can be programmed for rising edge or falling edge clocks through a dedicated pin. At a transmit clock frequency of 135MHz, 18bits of RGB data and 3bits of LCD timing and control data (HSYNC, VSYNC, DE) are transmitted at a rate of 945Mbps per LVDS data channel. The CL12451IP transmitter is an ideal means to solve EMI and cable size problems associated with wide, high-speed CMOS interfaces.

## **Feature**

- Input Clock: 20MHz to 135MHz (max: 170MHz) shift clock support

- Output Clock: 20MHz~135MHz Output Data Rate: 140Mbps~945Mbps (max: 1.19Gbps)

- Low power single 3.3V (Option: 2.8V) (Option: 1.0 / 1.2 / 1.8V Logic/Level Shifter)

- Clock edge programmable

- Supports VGA, SVGA, XGA, SXGA, SXGA+

- Narrow bus reduces cable size

- PLL requires no external components

- Power down mode

- 345mV swing LVDS for low EMI

- Supports 200mV Differential Amplitude Outputs

## **Block Diagram**